Imec reveals latest RF interposer tech

MmWave (30-100GHz) and sub-THz (100-300GHz) bands are seen as the future for next-generation RF systems including wireless data centres, automotive radar, optical transceivers, and ultra-high-speed short range wireless USB.

However, unlocking the potential of these higher frequencies means combining the high output power and drive capabilities of III/V materials with the scalability and cost-efficiency of CMOS technology – all integrated on a single carrier.

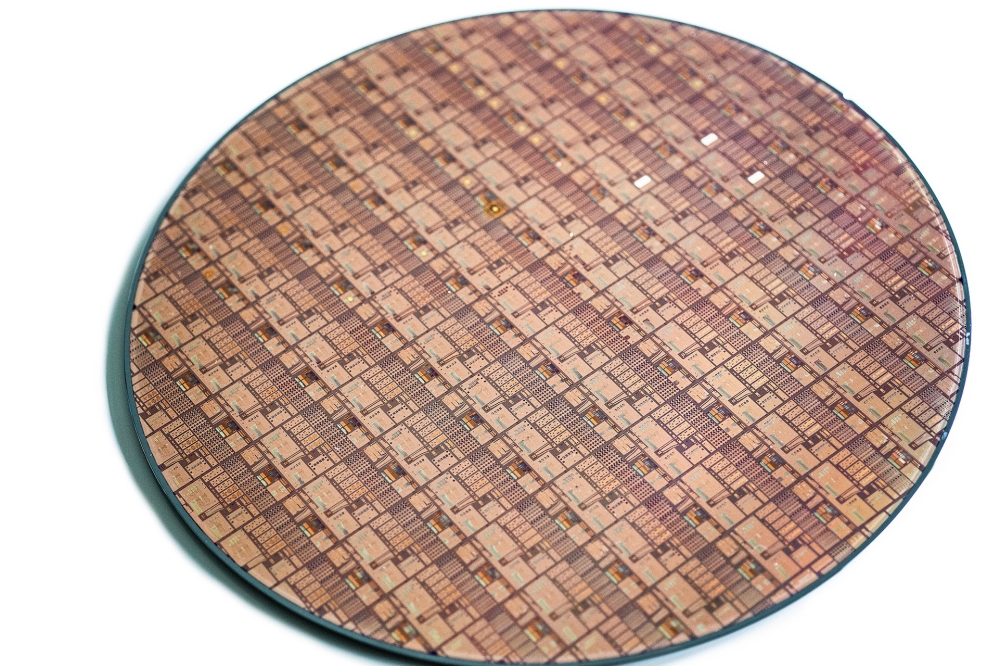

At the IEEE ECTC 2025 conference, Imec is highlighting its next generation solution for these applications: a 300mm RF silicon interposer platform that enables integration of RF-to-sub-THz CMOS and III/V chiplets on a single carrier. The platform achieves a record-low insertion loss of just 0.73dB/mm at frequencies up to 325GHz.

At last year’s IEDM, Imec reported a breakthrough in the hetero-integration of InP chiplets on a 300mm RF Si interposer – at frequencies only up to 140GHz. This recent announcement is the latest incarnation of the technology.

“What sets our approach apart is the ability to mix and match digital, RF-to-sub-THz CMOS technology nodes with a wide variety of III/V chiplets – not limited to InP, but also including SiGe, GaAs, and others,” said Xiao Sun, principal member of technical staff at Imec.

The platform’s digital interconnects benefit from Cu damascene back-end-of-line (BEOL) processing, while mmWave signal paths employ transmission lines on a low-loss RF polymer layer. Additionally, high-quality passive components – such as inductors – are integrated directly onto the RF silicon interposer, reducing the active chip area, lowering costs, and ensuring compact, low-loss RF interconnects for improved performance.

Imec’s technology combines RF/microwave links (with 5µm line width and 5µm spacing), with high-density digital interconnects (with 1µm/1µm line/spacing), and a fine flip-chip pitch of 40µm – with efforts underway to scale down to 20µm. Together, these features enable high integration density and a compact footprint.

As a next step, Xiao Sun and her team are preparing to augment the platform with additional features – including through-silicon vias, back-side redistribution layers, and MIMCAPs for supply decoupling. In parallel, Imec is preparing to open its RF interposer R&D platform to partners for early assessment, system validation, and prototyping – amongst others by making it accessible via NanoIC, Imec’s sub-2nm pilot line as part of the EU Chips Act.