Towards defect-free SiC epiwafers

Helping to drive improvements in SiC power devices, advances in epitaxy are producing nearly defect-free layers of SiC on the carbon face, and those that that are free from basal plane dislocations on the silicon face.

BY NGUYEN XUAN SANG AND SHIV KUMAR FROM THE INSTITUTE OF MICROELECTRONICS, A-STAR, SINGAPORE, AND MARCIN ZIELINSKI OF SOITEC, FRANCE

By surpassing the performance limits of silicon devices, those made from SiC are capturing an increasing share of the power electronics market. However, the high cost of this wide bandgap semiconductor is still a headwind to success, with the price of devices exacerbated by yield losses that can be traced back to defects in the substrate and the epitaxial layers.

There are various types of defects that arise in SiC, due to the material’s intrinsic physical properties. Defects include micropipes, triangles, carrots, stacking faults, and dislocations. For the latter class of imperfection, the main forms are basal plane dislocations, threading screw dislocations, and threading edge dislocations. Among them, basal plane dislocations are considered critical ‘killer defects’, because they induce bipolar degradation in SiC power devices.

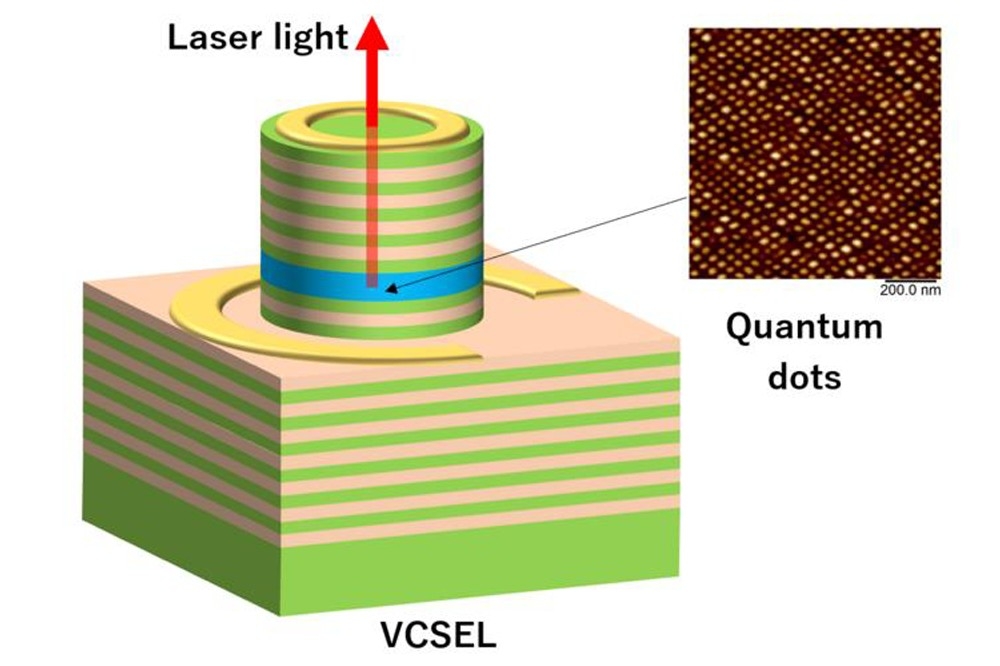

Figure 1. (a) The basic structural unit of a SiC crystal and (b) typical design of SiC trench MOSFET.

Over the years, there has been significant progress in SiC bulk growth and substrate production, in terms of both wafer size and defect reduction. Regarding the former, manufacturers of SiC wafers are rapidly transitioning to 200 mm production.

A key milestone in the sublimation process used to produce bulk SiC came in 2004, when Daisuke Nakamura and colleagues from Toyota Central R&D Laboratories, Japan, reported in a Nature paper the creation of seed that is free from micropipes and has very few dislocations. This advance opened the door to stable, optimised sublimation growth on high-quality seed layers. Thanks to this breakthrough, today’s commercially available 150 mm and 200 mm SiC substrates are micropipe-free, and exhibit low dislocation densities: basal plane dislocations are less than 500 cm-2, and threading edge and screw dislocations are both below 5,000 cm-2.

Due to the polarisation of the Si-C bond, the top surface of SiC can exhibit either silicon-face or carbon-face polarity. These two polarities result in distinct surface characteristics and different properties. In terms of oxidation, the carbon-face has a higher oxidation rate than the silicon-face. This difference, attributed to the higher concentration of dangling bonds on the carbon-face, complicates passivation during the oxidation process. Another noteworthy difference is that carbon-face samples often exhibit 4H-SiC polytype inclusions that extend through the entire wafer, whereas silicon-face samples are typically free from such inclusions. Surface roughness also differs, with the silicon-face tending to have a rougher surface, with a higher density of cracks, particularly near the edges.

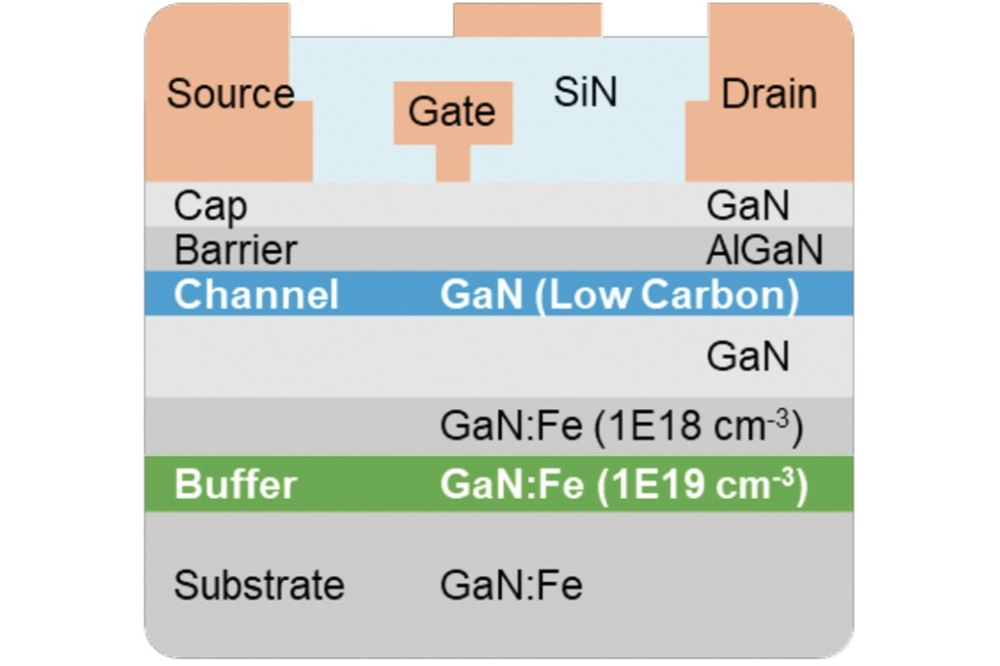

Figure 2. (a) Structure of SiC epitaxy growth on a 150 mm carbon-face

SiC substrate. (b) Typical surface morphology scan by atomic force

microscopy, determining a root-mean-square roughness, Rq, of around 0.28 nm. (c) Capacitance-voltage characteristics and calculated doping of SiC epilayer measured by a mercury probe.

Benefits of the carbon-face

Today’s SiC high-power device technology primarily utilises silicon-face SiC substrates. This face ensures a high-quality interface and a large band-offset with the gate oxide. However, in SiC trench MOSFETs, the gate stack is formed on the SiC (113) plane for both silicon-face and carbon-face substrates (see Figure 1).

For trench MOSFETs, the carbon-face presents advantages, due to its faster oxidation rate. This characteristic enables the formation of an oxide layer at the trench bottom that is up to three times thicker than that on the sidewalls, simplifying fabrication and improving the gate breakdown voltage. These strengths are realised despite the lower band-offset between SiO2 and carbon-face SiC.

Helping to maximise the performance of devices using the carbon-face is our partnership between A-STAR, the National University of Singapore, and Soitec. Working together, we have demonstrated a nearly defect-free carbon-face SiC epitaxy growth process with an incredibly high growth rate – it’s around 50 µm hr-1 on 150 mm carbon-face SiC substrates.

For this work, we loaded an epi-ready, n-type carbon-face SiC 150 mm substrate with a 4° off-cut towards (11

Using Fourier transform infrared spectroscopy, we confirmed the thicknesses of the buffer and drift layers, and determined that the thickness uniformity is less than 3 percent (see Figure 2 (a)). According to atomic force microscopy, our epiwafers have a smooth surface, with a root-mean-square roughness just below 0.3 nm.

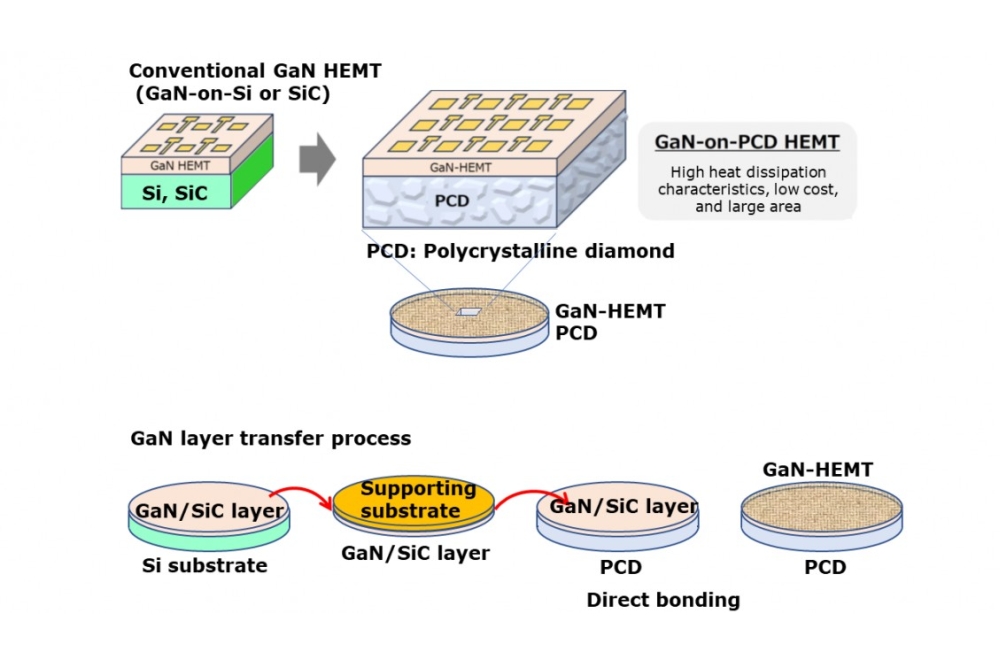

Figure 3. (a-c) Defect distribution and calculated yield in two

carbon-face SiC wafers, obtained with a Candela 8520 scan. (d) Total

killer defect density of the wafers, nearly defect-free obtained in

carbon-face SiC epitaxy. (e) Benchmarking the killer defect density of

carbon-face epitaxy with silicon-face epitaxy.

We have also investigated the electrical properties of our epiwafers. This has involved acquiring capacitance-voltage plots with a mercury-probe, and calculating doping profiles, derived from capacitance-voltage data (see Figure 2 (c)). Our results reveal that unintentional (or background) doping in the carbon-face SiC epilayer is around 1.5 x 1015 cm-3, a value low enough to enable precise control of doping in the drift layer within the range of 1-2 x 1016 cm-3 for MOSFET devices.

Using the KLA Candela 8520 system, we have measured the defect density in our carbon-face SiC epiwafers. This tool, which combines surface and photoluminescence defect analysis, has determined that there a very few defects in our material – the defect density of less than 0.1 cm-2 (see Figures 3 (a-d)).

To benchmark our carbon-face SiC epiwafers, we have compared them with a silicon-face SiC epilayer and a reference carbon-face SiC epi layer (see Figure 3 (e)). Compared with these two, the defect density in our carbon-face SiC epiwafers is nearly an order of magnitude lower, illustrating that our growth process produces material nearly free from defects. This low defect density provides significant advantages for carbon-face SiC devices, particularly in large-scale device architectures, such as bipolar devices.

Figure 4. (a) The chemical mechanical polishing (CMP) process on a SiC

wafer and the sub-surface damages observed on the wafer’s flat surface.

(b) Illustration of the oxidation process in carbon-face and

silicon-face SiC, highlighting how the faster oxidation rate of the

carbon-face SiC contributes to a higher material removal rate during the

CMP process of SiC wafers.

A key contributor to our nearly defect-free epitaxy is our dramatic reduction in pre-existing surface and sub-surface crystal defects in the SiC substrate. We have realised this by optimising our chemical mechanical polishing process, which involves oxidation and oxide removal (see Figure 4 (a) and (b) for an illustration of this process). Our approach is customised for carbon-face SiC, which has a far higher oxidation rate than that on the silicon face. By tailoring the chemical mechanical polishing process, we produce smooth surfaces with minimal sub-surface damage.

The most prominent defects occurring during the epitaxial process are basal plane dislocations and stacking faults. To minimise these imperfections, most basal plane dislocations, which have a defect density of around 500 cm-2, are converted to threading edge dislocations. Employing an optimised hydrogen gas etching process prevents conversion of the basal plane dislocations into more troublesome Shockley stacking faults (see Figure 5 (a)). Conversion of basal plane dislocations into threading edge dislocations is also promoted by the high growth rate of 50 µm hr-1, ensuring further minimisation of basal plane dislocations in the SiC epilayer.

Another asset of carbon-face epitaxy is favourable step-flow growth, thanks to the long diffusion length – it is greater than 1 µm (see Figure 5 (b)). Due to this, along with the high degree of conversion of basal plane dislocations into threading edge dislocations, we are able to enjoy nearly defect-free carbon-face SiC epitaxy.

Figure 5. (a) Conversion of basal plane dislocations (BPDs) in SiC epitaxy and (b)step-controlled epitaxy process.

Strengthening silicon-face epitaxy

In addition to our development of the epitaxy process on carbon-face SiC wafers, which has demonstrated the significant potential for defect reduction in SiC epitaxial growth, we have introduced innovations to the traditional epitaxy process on silicon-face SiC wafers. We have developed these breakthroughs on 200 mm SiC wafers. Key to our success is the conversion of basal plane dislocations in the substrate to threading edge dislocations in the buffer layer, prior to the growth of the device drift layer.

Our success builds on the work of Tangali Sudarshan’s group from the University of South Carolina. Back in 2005, in Applied Physics Letters (87 151913), they reported that epitaxy can be free from basal plane dislocations by etching the substrate surface with potassium hydroxide prior to loading the wafer into the processing chamber. The disadvantage of that particular process is that it’s impractical for large-scale production of SiC epiwafers. But there is much merit in the principle of preparing the surface by etching around the regions with basal plane dislocations, to promote their conversion to threading edge dislocations during epitaxial growth.

Figure 6. (a) Defect distribution and classification for 200 mm SiC

epitaxy, captured by the KLA Candela 8520 measurement for a batch of

eight wafers. (b) Defect density plot for these wafers, showing

extremely low defect density and a nearly basal-plane-dislocation-free

silicon-face SiC epitaxy layer.

Drawing on this approach, we have developed an in-situ etching technique for SiC wafers that involves the introduction of two etching steps: one during baking, and another between the buffer layer growth steps. The combination of in-situ hydrogen etching at processing temperatures and surface recovery through etch-back and material recovery via low-temperature baking is effective at filtering out basal plane dislocations in the drift layer. Material produced by this process, which is practical and scalable for SiC epitaxy manufacturing, is almost 100 percent free of basal plane dislocations

The effectiveness of our approach is highlighted by defect scans that capture the surface and total defect distribution of a batch of eight SiC wafers. These scans, acquired with a KLA Candela 8520 tool, reveal that the basal plane dislocations in the wafers are nearly eliminated, with a density less than 0.05 cm-2 (see Figure 6). Another benefit of the process is a significant reduction in defect density, which falls from a typical value of 1.0 cm-2 to just 0.3 - 0.4 cm-2.

Figure 7. (a) Process flow of typical SmartSiC wafer fabrication from

Soitec. (b) Advanced process for Smart SiC wafers using carbon-face SiC

epitaxial layers.

Smart SiC substrates

Another approach to realising SiC epitaxial wafers that are free from basal plane dislocations is to start with substrates that do not have this imperfection. In this case, one potential candidate is SmartSiC, a material technology developed by Soitec.

This company’s engineered substrates have a foundation for epi-growth that’s formed through wafer bonding and layer transfer (see Figure 7 (a)). These substrates are produced by bonding carbon-face donor SiC wafers onto heavily doped poly-SiC substrates. After splitting a mono-crystalline SiC wafer, a layer of approximately 1 µm of SiC single crystal remains on the poly-crystalline SiC, forming a new type of SiC wafer known as Smart SiC.

One of the biggest benefits of Smart SiC is the higher substrate doping of the poly-crystalline SiC – this simplifies the SiC MOSFET fabrication process, by enabling a straightforward backside ohmic contact and reducing the on-resistance in SiC MOSFETs. However, there are additional merits of SmartSiC, relating to switching donor wafers from mono-SiC to a carbon-face epitaxial layer that’s bonded to a poly-SiC substrate (see Figure 7 (b)). With this modification, the transfer layer in the SmartSiC wafers originates from the carbon-face SiC epitaxial layer, and retains its associated advantages.

Figure 8. (a) Defect density of a heavily doped carbon-face SiC epitaxial layer scanned using the KLA Candela 8520 system. The two wafers are free from basal plane dislocations. (b) Doping distribution along the X-direction of the carbon-face SiC epitaxial layer, showing a doping level exceeding 6 x 1018 cm-3.

To be used as a donor wafer for Smart SiC, the carbon-face SiC epitaxial layer must exhibit a low defect density and high doping levels.

According to characterisation provided by the KLA Candela 8520 tool, the wafers we have developed in this work meet these criteria, exhibiting an extremely low defect density that’s free from basal plane dislocations.

Doping measurements for these wafers indicate values exceeding 6 x 1018 cm-3, showing that SmartSiC technology is a promising new approach for producing SiC MOSFETs.

While SiC wafers still have some way to go to become ‘defect-free’, as is the case for silicon epiwafers, much progress is being made in this direction – and our work provides another significant step along this path.

•The authors wish to thank Lakshmi Kanta Bera, Chand Umesh, Surasit Chung, Navab Singh, Gong Xiao and Yeo Yee-Chia from the Institute of Microelectronics, A-Star, Tok Eng Soon from the National University of Singapore, and Shian Yeu Kam, Loic Kabelaan, Walter Schwarzenbach, Ionut Radu and Loann Boudin of Soitec, France